Portfolio

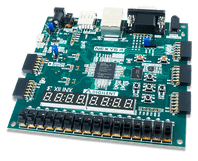

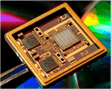

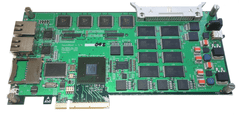

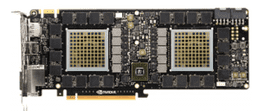

Three broad approaches are under development. We have a business partnership with General Vision, Inc. to utilize their proprietary digital neurons in the form of IP, which we also license for on-shore and federal purposes. Having been involved in the development process for the Berkeley RISC-V ISA, we are pairing those neurons with and open-souce core to create a low-power NeuroSOC (both as a package-scale device as well as dedicated silicon), including the Linux API for access. For datacenter and HPC deployment, we are designing the second-generation PCIe acceleration hardware, targeting individual 1-32K neuron chips initially but expanding to wafer-scale MCMs. Several applications have been deployed on test hardware by our collaborators: industrial inspection, components of autonomous vehicle operation, and latent semantic analytics.